Simulation and Design of Super Junction VDMOS Devices Using Nuwa TCAD Software

GMPT, October 2024

Abstract: Vertical Double-Diffused Metal Oxide Semiconductor Field Effect Transistor (VDMOS) is a unipolar power switching device with advantages of fast switching speed and high static input impedance. It is widely used in motor speed control, radar, switching power supplies, automotive electronics, inverters, and mobile communication. Super-junction VDMOS introduces a super-junction structure based on traditional VDMOS, replacing the lightly doped structure in the drift region. When the device is in a reverse-biased state, under the influence of the transverse electric field, the charges of the N-type semiconductor and P-type semiconductor in the super-junction region are mutually compensated and depleted, forming a transverse voltage-sustaining layer and enhancing the device’s reverse breakdown voltage.

This article presents the simulation of a super-junction VDMOS device using Nuwa TCAD software and showcases the simulation results.

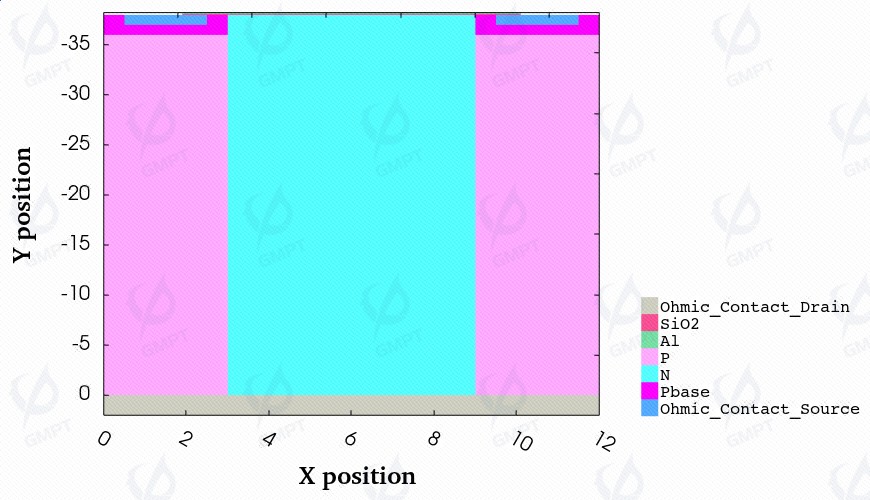

1. Device Structure

In this work, the super-junction VDMOS device structure is shown in Figure 1. The P-pillar height is set to 36 μm, the cell width is set to 12 μm, and the doping concentrations are set as follows: pillar region at , P-base region at , drain region at , and source region at . The gate oxide thickness is set to 0.1 μm. (Some simulation data in this article are sourced from reference [1].)

2. Physical Model Settings

2.1 Continuity Equations

2.2 Poisson Equation

2.3 Low-Field and High-Field Mobility Models

Low-Field Mobility Model (Masetti Model):

High-Field Mobility Model (Canali Model):

2.4 Interface Trap Model

Exponential Tail Model:

Gaussian Model:

2.5 Bulk Trap Model

Shockley-Read-Hall Model:

Gaussian Model:

2.6 Impact Ionization Model

- Okuto Model:

3. Results and Discussion

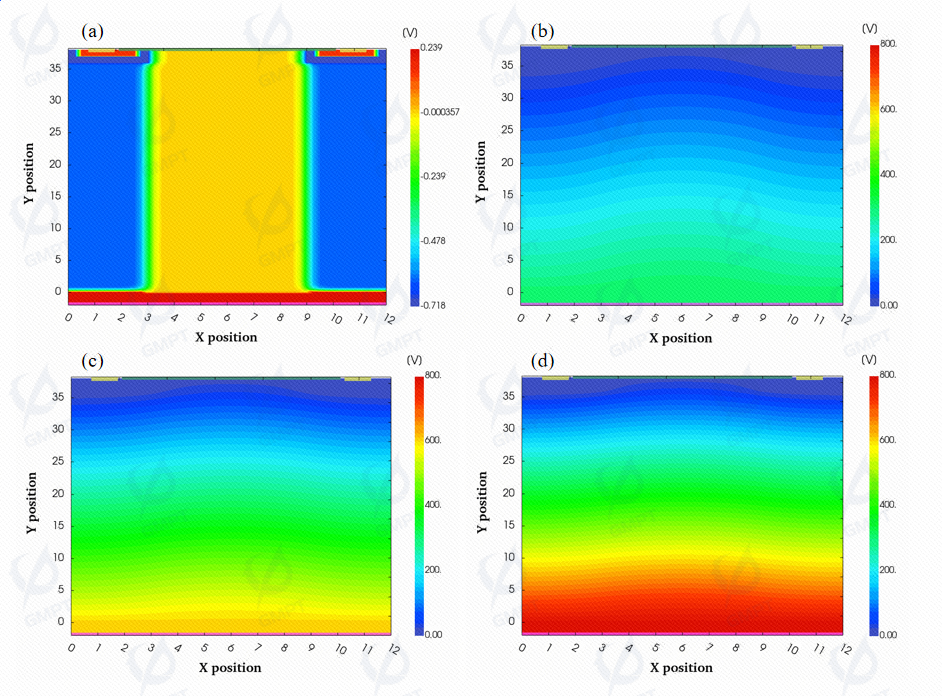

3.1 Reverse Voltage Distribution

The figure above shows the potential distribution of the super-junction VDMOS device from equilibrium to reverse breakdown under reverse bias.

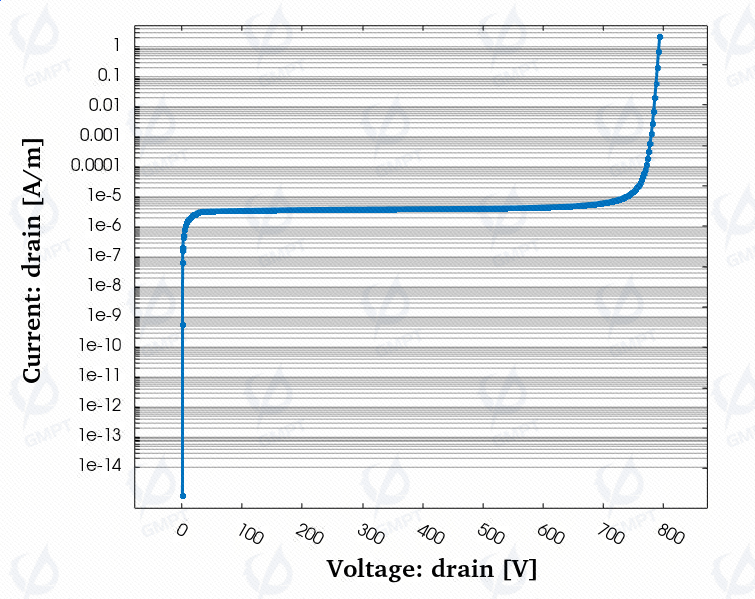

3.2 Reverse Breakdown Characteristics

As shown in the figure, the drain current is approximately before reverse breakdown, then sharply increases near the breakdown voltage due to avalanche breakdown, with a reverse breakdown voltage around 790V.

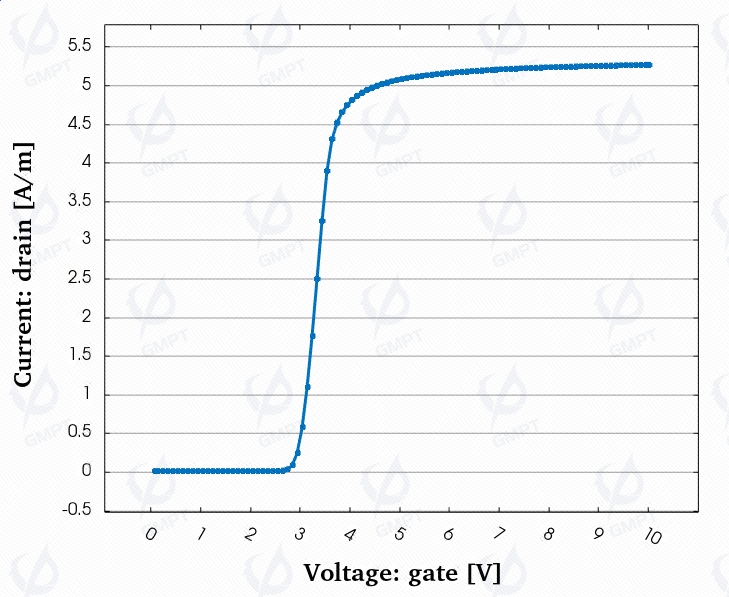

3.3 Threshold Voltage

The threshold voltage of the super-junction VDMOS device is approximately 2.8V.

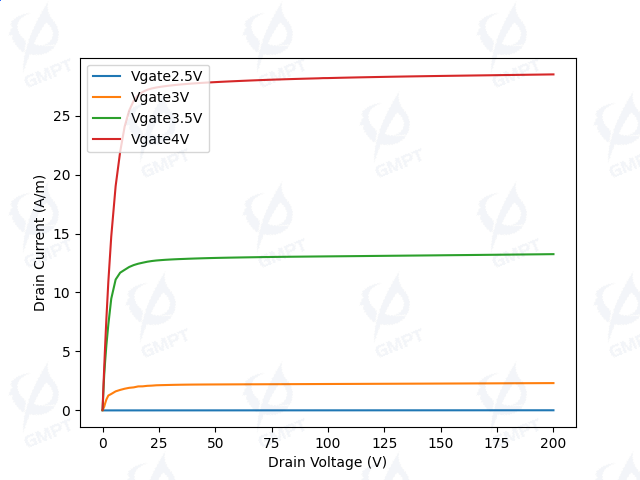

3.4 Transfer Characteristics

Figure 5 illustrates the transfer characteristics of the super-junction VDMOS device at gate voltages of 2.5V, 3V, 3.5V, and 4V. Since the threshold voltage of the device is 2.8V, the device channel is not open when the gate voltage is 2.5V, and there is no forward output. When the gate voltage exceeds the threshold voltage, the device channel opens, and the forward output increases with the gate voltage, while the drain current tends to saturate as the drain voltage increases.

4. Conclusion

This article presents the simulation process and results for a super-junction VDMOS device. It includes an introduction to the physical models applied in the simulation, along with key simulation results such as reverse voltage distribution, reverse breakdown characteristics, threshold voltage, and transfer characteristics under different gate voltages.

References

[1] Lyuqiang Li, "Process Window Improvement and Reliability Enhancement of Super-junction Devices," Master's thesis, University of Electronic Science and Technology of China.